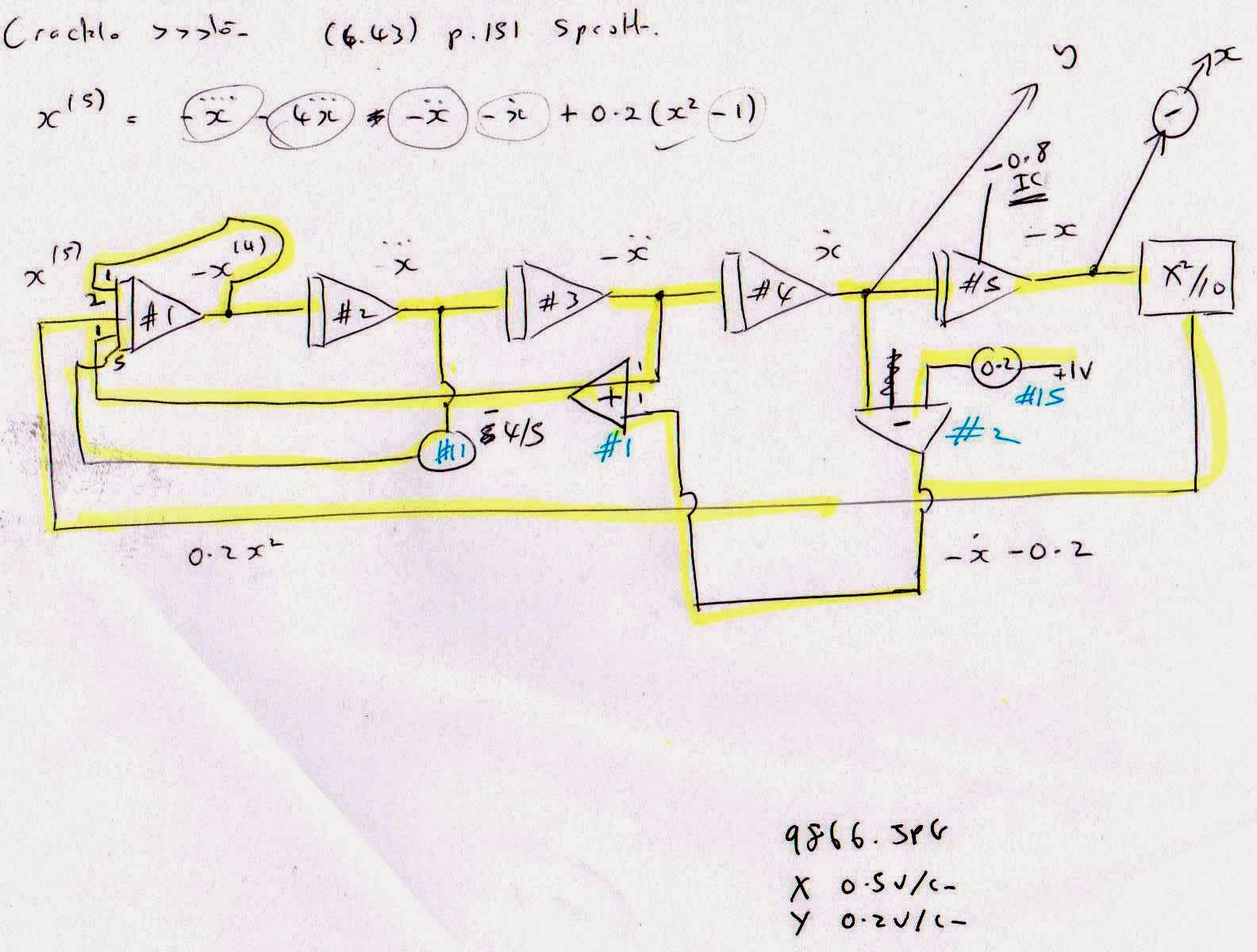

I came across [1] the Rucklidge oscillator, the equations for which are:

In the above, I've included a scaling parameter α (setting α = 1 gives the original equations; for my computer, setting α= 5 gave an appropriate down scaling of the solution (so it fits within +/- 10 V)).

Reference [1] gives results for various values of constants κ and λ - the behavior of the solution depends strongly on these - in particular, it is interesting to plot the solution either side of (something called) the homoclinic bifurcation (Figure 6 of reference [1]).

I plotted the results for three values of λ (blue = -2.5; red = -3.15; green = -6.0). In all cases κ = -1.724, (corresponding to Rucklidge's B point).

The blue curve (λ = -2.5) corresponds to region I of reference [1] - a 'gluing bifurcation'; the red curve (λ = -3.15) and green curve (λ = -6.0) are in region II - a 'homoclinic explosion'. All solutions share the same initial condition (v0 = 0.4). Evidently, the solution does indeed descend into chaos, as λ is made more negative.

Fascinating stuff.

Reference

[1] Rucklidge, A.M. (1992) Chaos in models of double convection. Journal of Fluid Mechanics, 237. pp. 209-229.

In the above, I've included a scaling parameter α (setting α = 1 gives the original equations; for my computer, setting α= 5 gave an appropriate down scaling of the solution (so it fits within +/- 10 V)).

Reference [1] gives results for various values of constants κ and λ - the behavior of the solution depends strongly on these - in particular, it is interesting to plot the solution either side of (something called) the homoclinic bifurcation (Figure 6 of reference [1]).

I plotted the results for three values of λ (blue = -2.5; red = -3.15; green = -6.0). In all cases κ = -1.724, (corresponding to Rucklidge's B point).

The blue curve (λ = -2.5) corresponds to region I of reference [1] - a 'gluing bifurcation'; the red curve (λ = -3.15) and green curve (λ = -6.0) are in region II - a 'homoclinic explosion'. All solutions share the same initial condition (v0 = 0.4). Evidently, the solution does indeed descend into chaos, as λ is made more negative.

Fascinating stuff.

|

| vw-plane (w is vertical), both axes 0.2 V/cm |

|

| uw-plane (w is vertical), both axes 0.2 V/cm |

[1] Rucklidge, A.M. (1992) Chaos in models of double convection. Journal of Fluid Mechanics, 237. pp. 209-229.